电源完整性设计(5)实际电容的特性

2010/03/18 19:47 于 于博士专栏

正确使用电容进行电源退耦,必须了解实际电容的频率特性。理想电容器在实际中是不存在的,这就是为什么经常听到“电容不仅仅是电容”的原因。

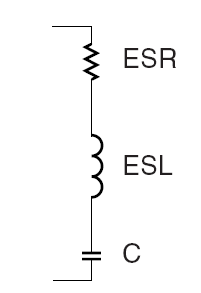

实际的电容器总会存在一些寄生参数,这些寄生参数在低频时表现不明显,但是高频情况下,其重要性可能会超过容值本身。图4是实际电容器的SPICE模型,图中,ESR代表等效串联电阻,ESL代表等效串联电感或寄生电感,C为理想电容。

图4 电容模型

等效串联电感(寄生电感)无法消除,只要存在引线,就会有寄生电感。这从磁场能量变化的角度可以很容易理解,电流发生变化时,磁场能量发生变化,但是不可能发生能量跃变,表现出电感特性。寄生电感会延缓电容电流的变化,电感越大,电容充放电阻抗就越大,反应时间就越长。等效串联电阻也不可消除的,很简单,因为制作电容的材料不是超导体。

讨论实际电容特性之前,首先介绍谐振的概念。对于图4的电容模型,其复阻抗为:

(公式3)

当频率很低时, 远小于

远小于 ,整个电容器表现为电容性,当频率很高时,

,整个电容器表现为电容性,当频率很高时,  大于

大于  ,

,

电容器此时表现为电感性,因此“高频时电容不再是电容”,而呈现为电感。当 时,

时, ,此时容性阻抗矢量与感性阻抗之差为0,电容的总阻抗最小,表现为纯电阻特性。该频率点就是电容的自谐振频率。自谐振频率点是区分电容是容性还是感性的分界点,高于谐振频率时,“电容不再是电容”,因此退耦作用将下降。因此,实际电容器都有一定的工作频率范围,只有在其工作频率范围内,电容才具有很好的退耦作用,使用电容进行电源退耦时要特别关注这一点。寄生电感(等效串联电感)是电容器在高于自谐振频率点之后退耦功能被消弱的根本原因。图5显示了一个实际的0805封装0.1uF陶瓷电容,其阻抗随频率变化的曲线。

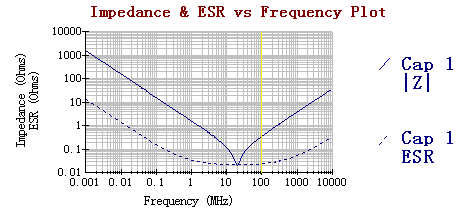

,此时容性阻抗矢量与感性阻抗之差为0,电容的总阻抗最小,表现为纯电阻特性。该频率点就是电容的自谐振频率。自谐振频率点是区分电容是容性还是感性的分界点,高于谐振频率时,“电容不再是电容”,因此退耦作用将下降。因此,实际电容器都有一定的工作频率范围,只有在其工作频率范围内,电容才具有很好的退耦作用,使用电容进行电源退耦时要特别关注这一点。寄生电感(等效串联电感)是电容器在高于自谐振频率点之后退耦功能被消弱的根本原因。图5显示了一个实际的0805封装0.1uF陶瓷电容,其阻抗随频率变化的曲线。

图5 电容阻抗特性

电容的自谐振频率值和它的电容值及等效串联电感值有关,使用时可查看器件手册,了解该项参数,确定电容的有效频率范围。下面列出了AVX生产的陶瓷电容不同封装的各项参数值。

封装 ESL(nH) ESR(欧姆)

0402 0.4 0.06

0603 0.5 0.098

0805 0.6 0.079

1206 1 0.12

1210 0.9 0.12

1812 1.4 0.203

2220 1.6 0.285

电容的等效串联电感和生产工艺和封装尺寸有关,同一个厂家的同种封装尺寸的电容,其等效串联电感基本相同。通常小封装的电容等效串联电感更低,宽体封装的电容比窄体封装的电容有更低的等效串联电感。

既然电容可以看成RLC串联电路,因此也会存在品质因数,即Q值,这也是在使用电容时的一个重要参数。

电路在谐振时容抗等于感抗,所以电容和电感上两端的电压有效值必然相等,电容上的电压有效值UC=I1/ωC=U/ωCR=QU,品质因数Q=1/ωCR,这里I是电路的总电流。电感上的电压有效值UL=ωLI=ωLU/R=QU,品质因数Q=ωL/R。因为:UC=UL 所以Q=1/ωCR=ωL/R。电容上的电压与外加信号电压U之比UC/U=(I*1/ωC)/RI=1/ωCR=Q。电感上的电压与外加信号电压U之比UL/U=ωLI/RI=ωL/R=Q。从上面分析可见,电路的品质因数越高,电感或电容上的电压比外加电压越高。

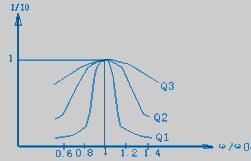

图6 Q值的影响

Q值影响电路的频率选择性。当电路处于谐振频率时,有最大的电流,偏离谐振频率时总电流减小。我们用I/I0表示通过电容的电流与谐振电流的比值,即相对变化率。 表示频率偏离谐振频率程度。图6显示了I/I0与点击在新窗口中浏览此图片 关系曲线。这里有三条曲线,对应三个不同的Q值,其中有Q1>Q2>Q3。从图中可看出当外加信号频率ω偏离电路的谐振频率ω0时,I/I0均小于1。Q值越高在一定的频偏下电流下降得越快,其谐振曲线越尖锐。也就是说电路的选择性是由电路的品质因素Q所决定的,Q值越高选择性越好。

在电路板上会放置一些大的电容,通常是坦电容或电解电容。这类电容有很低的ESL,但是ESR很高,因此Q值很低,具有很宽的有效频率范围,非常适合板级电源滤波。