2010/03/20 21:32 于 于博士专栏

难得半日清闲,看到留言板有网友留言问道这个问题,留一篇随笔,与各位网友共享。

当我们提到特性阻抗的时候,通常很少考虑它与频率的关系。其原因在于,特性阻抗是传输线的一个相当稳定的属性,主要和传输线的结构也就是横截面的形状有关。从工程的角度来说,把特性阻抗作为一个恒定量是合理的。说实话,搞了这么长时间的SI设计,还没碰到需要考虑特性阻抗变化的情况。

既然有网友一定要考虑这个问题,今天我们就稍稍深入一下,看看特性阻抗的真实面目。虽然没有太大的工程应用价值,但是对于理解问题还是有好处的。

特性阻抗是从理论上分析传输线时经常提到的一个量,从传输线的角度来说,它可以用下面的公式表示:

Z0 = / L

/ ------

^/ C

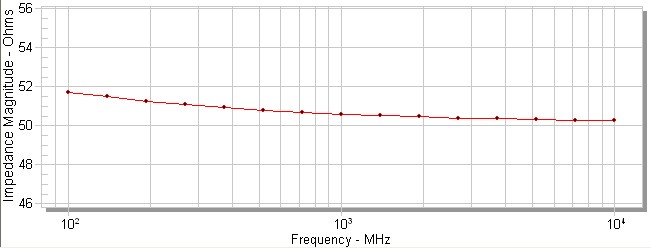

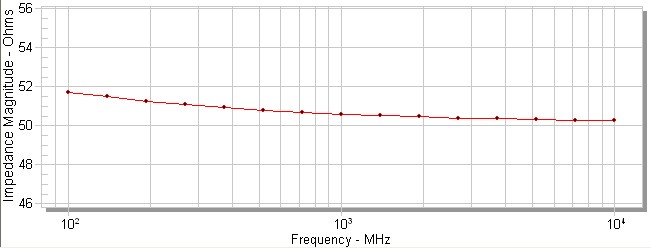

L表示传输线的单位长度电感,C为单位长度电容。乍一看,似乎公式中没有任何变化的量。但是特性阻抗真的是个恒定的量吗?我们使用Polar软件对横截面固定的传输线进行扫频计算,频率范围定在100MHz~10GHz,来看看场求解器给出的结果,如下图:

你可能感到惊讶,特性阻抗随着频率的升高变小了,why?阻抗公式中那个量发生了变化?

其实这涉及到电磁学方面的一个深层次的问题。罪魁祸首是电感!!电感问题是个很复杂的问题,对电感的理论计算很繁琐,有兴趣的网友可以找资料看看电感的计算,详细的推导过程我就不在这里写了。简单的说,导线的电感由两部分组成:导线的内部电感和导线的外部电感。当频率升高时,导线的内部电感减小,外部电感不变,总电感减小,因而导致了特性阻抗减小。

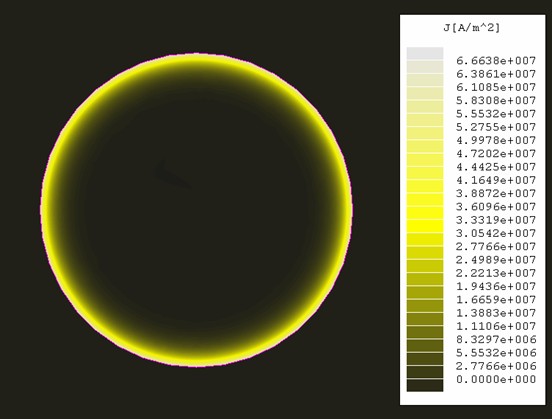

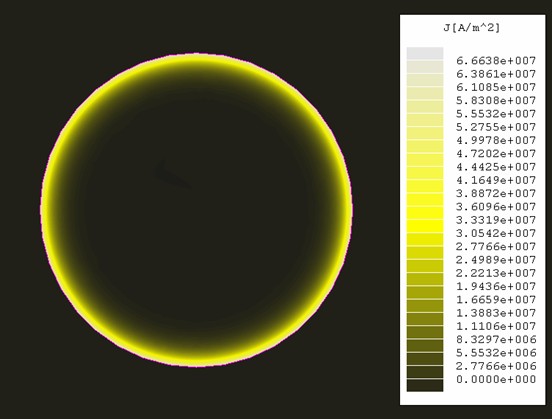

我们知道,电感的定义是指围绕在电流周围的磁力线匝数。电感随频率减小,直觉告诉我们一定是导线中电流分布发生了变化。到这里我想各位网友应该豁然开朗了。趋肤效应(skin effect)你一定不会陌生。看看下面的这张图你会有更直观的感受,这是用二维场求解器仿真出来的高频时导体中电流的分布。黄色部分是电流所在位置。

当频率升高时,电流向导线表面集中,在导线内部电流密度减小,当然电感减小。电感的本质,是围绕在电流周围的磁力线匝数,注意“围绕在电流周围”这个说法。假设存在极端情况,导线内部电流完全消失,所有的电流集中在导体表面,磁力线当然没法再内部去环绕电流,内部电感消失。导线总电感减小,减小的那一部分就是导线的内部电感。当然这种说法不严谨,不过对直观的理解问题非常有帮助。

结论:

1、传输线的特性阻抗确实和频率有关,随着频率升高,特性阻抗减小,但会逐渐趋于稳定。

2、特性阻抗的变化的原因是导线的单位长度电感随频率升高而减小。

3、这种特性阻抗的变化很小,在工程应用中一般不用考虑它的影响。知道有这个事就是了。

(文章转摘自:于博士信号完整性研究网 )

I Love the World!

2010/03/20 10:07 于 于博士专栏

很多时候,PCB走线中途会经过过孔、测试点焊盘、短的stub线等,都存在寄生电容,必然对信号造成影响。走线中途的电容对信号的影响要从发射端和接受端两个方面分析,对起点和终点都有影响。

首先按看一下对信号发射端的影响。当一个快速上升的阶跃信号到达电容时,电容快速充电,充电电流和信号电压上升快慢有关,充电电流公式为:I=C*dV/dt。电容量越大,充电电流越大,信号上升时间越快,dt越小,同样使充电电流越大。

我们知道,信号的反射与信号感受到的阻抗变化有关,因此为了分析,我们看一下,电容引起的阻抗变化。在电容开始充电的初期,阻抗表示为:

这里dV实际上是阶跃信号电压变化,dt为信号上升时间,电容阻抗公式变为:

从这个公式中,我们可以得到一个很重要的信息,当阶跃信号施加到电容两端的初期,电容的阻抗与信号上升时间和本身的电容量有关。

通常在电容充电初期,阻抗很小,小于走线的特性阻抗。信号在电容处发生负反射,这个负电压信号和原信号叠加,使得发射端的信号产生下冲,引起发射端信号的非单调性。

对于接收端,信号到达接收端后,发生正反射,反射回来的信号到达电容位置,那个样发生负反射,反射回接收端的负反射电压同样使接收端信号产生下冲。

为了使反射噪声小于电压摆幅的5%(这种情况对信号影响可以容忍),阻抗变化必须小于10%。那么电容阻抗应该控制在多少?电容的阻抗表现为一个并联阻抗,我们可以用并联阻抗公式和反射系数公式来确定它的范围。对于这种并联阻抗,我们希望电容阻抗越大越好。假设电容阻抗是PCB走线特性阻抗的k倍,根据并联阻抗公式得到电容处信号感受到的阻抗为:

阻抗变化率为: ,即

,即 ,也就是说,根据这种理想的计算,电容的阻抗至少要是PCB特性阻抗的9倍以上。实际上,随着电容的充电,电容的阻抗不断增加,并不是一直保持最低阻抗,另外,每一个器件还会有寄生电感,使阻抗增加。因此这个9倍限制可以放宽。在下边的讨论中假设这个限制是5倍。

,也就是说,根据这种理想的计算,电容的阻抗至少要是PCB特性阻抗的9倍以上。实际上,随着电容的充电,电容的阻抗不断增加,并不是一直保持最低阻抗,另外,每一个器件还会有寄生电感,使阻抗增加。因此这个9倍限制可以放宽。在下边的讨论中假设这个限制是5倍。

有了阻抗的指标,我们就可以确定能容忍多大的电容量。电路板上50欧姆特性阻抗很常见,我就用50欧姆来计算。

得出:

即在这种情况下,如果信号上升时间为1ns,那么电容量要小于4皮法。反之,如果电容量为4皮法,则信号上升时间最快为1ns,如果信号上升时间为0.5ns,这个4皮法的电容就会产生问题。

这里的计算只不过是为了说明电容的影响,实际电路中情况十分复杂,需要考虑的因素更多,因此这里计算是否精确没有实际意义。关键是要通过这种计算理解电容是如何影响信号的。我们对电路板上每一个因素的影响都有一个感性认识后,就能为设计提供必要的指导,出现问题就知道如何去分析。精确的评估需要用软件来仿真。

总结:

1 PCB走线中途容性负载使发射端信号产生下冲,接收端信号也会产生下冲。

2 能容忍的电容量和信号上升时间有关,信号上升时间越快,能容忍的电容量越小。

(文章转摘自:于博士信号完整性研究网 )

I Love the World!

2010/03/20 10:01 于 于博士专栏

信号的接收端可能是集成芯片的一个引脚,也可能是其他元器件。不论接收端是什么,实际的器件的输入端必然存在寄生电容,接受信号的芯片引脚和相邻引脚之间有一定的寄生电容,和引脚相连的芯片内部的布线也会存在寄生电容,另外引脚和信号返回路径之间也会存在寄生电容。

好复杂,这么多寄生电容!其实很简单,想想电容是什么?两个金属板,中间是某种绝缘介质。这个定义中并没有说两个金属板是什么形状的,芯片两个相邻引脚也可以看做是电容的两个金属板,中间介质是空气,不就是一个电容么。芯片引脚和PCB板内层的电源或地平面也是一对金属板,中间介质是PCB板的板材,常见的是FR4材料,也是一个电容。呵呵,搞来搞去,还是回到了最基础的部分。高手不要笑,太简单了。不过确实很多人看到寄生电容就感到有点晕,理解不透,所以在这里啰嗦一下。

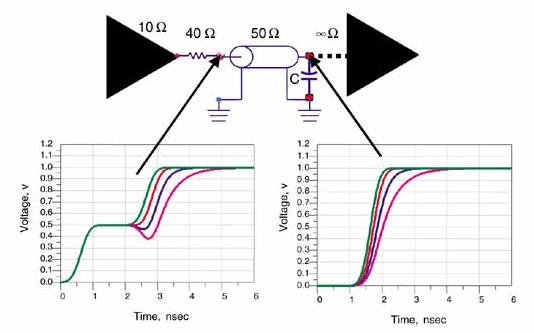

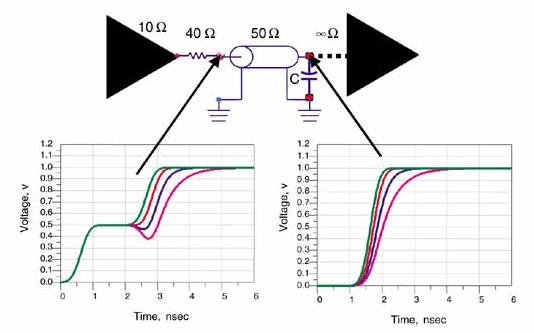

回到正题,下面研究一下信号终端的电容有什么影响。将模型简化,用一个分立电容元件代替所有寄生电容,如图1所示。

图1

我们考察B点电容的阻抗情况。电容的电流为:

随着电容的充电,电压变化率逐渐减小(电路原理中的瞬态过程),电容的充电电流也不断减小。即电容的充电电流是随时间变化的。

电容的阻抗为:

因此电容所表现出来的阻抗随时间变化,不是恒定的。正是这种阻抗的变化特性决定了电容对信号影响的特殊性。如果信号上升时间小于电容的充电时间,最初电容两端的电压迅速上升,这时阻抗很小。随着电容充电,电压变化率下降,充电电流减小,表现为阻抗明显增大。充电时间无穷大时,电容相当于开路,阻抗无穷大。

阻抗的变化必然影响信号的反射。在充电的开始一段时间,阻抗很小,小于传输线的特性阻抗,将发生负反射,反射回源端A点的信号将产生下冲。随着电容阻抗的增加,反射逐渐过渡到正反射,A点的信号经过一个下冲会逐渐升高,最终达到开路电压。

因此电容负载使源端信号产生局部电压凹陷。精确波形和传输线的特性阻抗、电容量、信号上升时间有关。

对于接收端,很明显,就是一个RC充电电路,不是很严谨,但是和实际情况非常相似。电容两端电压,即B点电压随RC充电电路的时间常数呈指数增加(基本电路原理)。因此电容对接收端信号上升时间产生影响。

RC充电电路的时间常数为 ,这是B点电压上升到电压终值的即37%所需的时间。B点电压10%~90%上升时间为

如果传输线特性阻抗为50欧姆,电容量10pF,则10~90充电时间为1.1ns。如果信号上升时间小于1.1ns,那么B点电压上升时间主要由电容充电时间决定。如果信号上升时间大于1.1ns,末端电容器作用是使上升时间进一步延长,增加约1.1ns(实际应比这个值小)。图2显示了终端电容负载对驱动端和接受端产生影响的示意图,放在这里,让大家能有个感性的认识。

图2

至于信号上升时间增加的精确值是多少,对于电路设计来说没必要,只要定性的分析,有个大致的估算就可以了。因为计算再精确也没实际意义,电路板的参数也不精确!对于设计者来说,定性分析并了解影响,大致估算出影响在那个量级,能给电路设计提供指导就可以了,其他的事软件来做吧。举个例子,如果信号上升时间1ns,电容使信号上升时间增加远小于1ns,比如0.2 ns,那么这么一点点增加可能不会有什么影响。如果电容造成的上升时间增加很多,那可能就会对电路时序产生影响。那么多少算很多?看看电路的时序余量吧,这涉及到电路的时序分析和时序设计。

总之接收端电容负载的影响有两点:

1、 使源端(驱动端)信号产生局部电压凹陷。

2、 接收端信号上升时间延长。

在电路设计中这两点都要考虑。

(文章转摘自:于博士信号完整性研究网 )

I Love the World!

,即

,即 ,也就是说,根据这种理想的计算,电容的阻抗至少要是PCB特性阻抗的9倍以上。实际上,随着电容的充电,电容的阻抗不断增加,并不是一直保持最低阻抗,另外,每一个器件还会有寄生电感,使阻抗增加。因此这个9倍限制可以放宽。在下边的讨论中假设这个限制是5倍。

,也就是说,根据这种理想的计算,电容的阻抗至少要是PCB特性阻抗的9倍以上。实际上,随着电容的充电,电容的阻抗不断增加,并不是一直保持最低阻抗,另外,每一个器件还会有寄生电感,使阻抗增加。因此这个9倍限制可以放宽。在下边的讨论中假设这个限制是5倍。