结束语

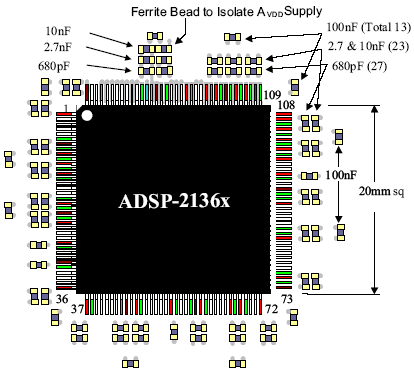

电源系统去耦设计要把引脚去耦和电源平面去耦结合使用已达到最优设计。时钟、PLL、DLL等去耦设计要使用引脚去耦,必要时还要加滤波网络,模拟电源部分还要使用磁珠等进行滤波。针对具体应用选择退耦电容的方法也很流行,如在电路板上发现某个频率的干扰较大,就要专门针对这一频率选择合适的电容,改进系统设计。总之,电源系统的设计和具体应用密切相关,不存在放之四海皆准的具体方案。关键是掌握基本的设计方法,具体情况具体分析,才能很好的解决电源去耦问题。

少长咸集

-

上一篇

电源完整性设计(16)电容的安装方法

发表于2010-03-19 浏览164 评论0

上一篇

电源完整性设计(16)电容的安装方法

发表于2010-03-19 浏览164 评论0

-

下一篇

电源完整性:电容的去耦时间

发表于2010-03-19 浏览141 评论0

下一篇

电源完整性:电容的去耦时间

发表于2010-03-19 浏览141 评论0

-

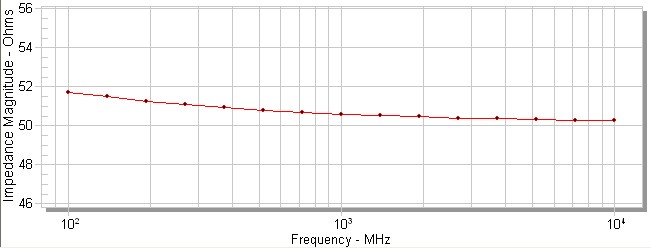

特性阻抗和频率有关吗?

浏览165 评论0

于博士专栏

特性阻抗和频率有关吗?

浏览165 评论0

于博士专栏

-

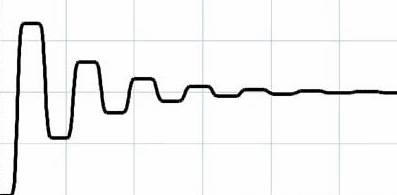

信号完整性:PCB走线中途容性负载反射

浏览167 评论0

于博士专栏

信号完整性:PCB走线中途容性负载反射

浏览167 评论0

于博士专栏

-

信号完整性:接收端容性负载的反射

浏览197 评论0

于博士专栏

信号完整性:接收端容性负载的反射

浏览197 评论0

于博士专栏

-

信号完整性:PCB走线宽度变化产生的反射

浏览171 评论0

于博士专栏

信号完整性:PCB走线宽度变化产生的反射

浏览171 评论0

于博士专栏

-

信号完整性:信号振铃是怎么产生的

浏览162 评论0

于博士专栏

信号完整性:信号振铃是怎么产生的

浏览162 评论0

于博士专栏

-

信号完整性:信号反射

浏览165 评论0

于博士专栏

信号完整性:信号反射

浏览165 评论0

于博士专栏

-

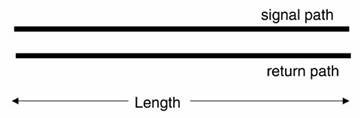

信号完整性:多长的走线才是传输线

浏览170 评论0

于博士专栏

信号完整性:多长的走线才是传输线

浏览170 评论0

于博士专栏

-

信号完整性:特性阻抗

浏览173 评论0

于博士专栏

信号完整性:特性阻抗

浏览173 评论0

于博士专栏

-

信号完整性研究:理解临界长度

浏览193 评论0

于博士专栏

信号完整性研究:理解临界长度

浏览193 评论0

于博士专栏

-

信号完整性研究:反射现象

浏览162 评论0

于博士专栏

信号完整性研究:反射现象

浏览162 评论0

于博士专栏